SPARC Architecture

Based on "The SPARC Architecture Manual:

Version 8", SPARC International

Introduction to SPARC Architecture

SPARC is a RISC computer architecture. RISC stands for "Reduced Instruction

Set Computer".

Such computers use few instructions with a fixed size, which is usually

the size of the word in the architecture.

A word is the most common number of bytes used to represent

a piece of information.

The few uniform size instructions used in that type of architecture

allow for building simpler and faster machines.

The simplicity comes from the need of fewer hardware units to implement

the instructions.

The speed gain comes from the use of pipelining - executing several

instructions at their different stages of execution

simultaneously.

Register Files

Registers are memory cells located on the CPU (Central Processing Unit)

chip.

In this architecture there are 32 general purpose integer registers

and 32 floating point registers.

The small number of registers makes access to these is very fast, which

is important for speeding up program execution.

Integer General Purpose Register File

The 32 general purpose integer registers are named from %r0 to %r31. They

also have aliases according to the different role they play

in a program's execution:

%g0 .. %g7 global registers; same as %r0 .. %r7

%o0 .. %o7 out registers;

same as %r8 .. %r15

%l0 .. %l7 local registers;

same as %r16 .. %r23

%i0 .. %i7 in

registers; same as %r24 .. %r31

%r0 is always 0

Floating-Point Register File

Floating-Point registers have the names: %f0 .. %f31. They are used to

hold real numbers.

When a bigger number is needed to be stored, they can be used in pairs

and groups of four.

Special Symbol Names

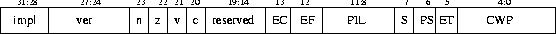

%psr Processor State Register

The processor state register has the following structure:

Condition Code Bits

Condition code bits are part of %psr. They are set during execution of

some assembly instructions. Their contents can be checked afterwards and

acted upon,

N is set if result of arithmetic operation (cc version of an

instruction) has a most significant bit 1.

Z is set if result of arithmetic operation (cc version

of an instruction) is zero.

%wim Window Invalid Mask Register

%tbr Trap Base Register

%y Y register

The %y register is used for multiplication and division. It holds the 32

most significant bits of the dividend in division and the 32 most significant

bits of the result in multiplication.

%fsr Floating-Point State Register

Floating Point Condition Codes

E 0 if fregrs1=fregrs2

L 1 if fregrs1<fregrs2

G 2 if fregrs1>fregrs2

U 3 if fregrs1 ? fregrs2 (unordered -

one or both of the numbers were NaN )

%csr Coprocessor-State Register

%fq Floating-Point Queue

%cq Coprocessor Queue

%hi

Unary operator which extracts high 22 bits of its operand.

%lo

Unary operator which extracts low 10 bits of its operand.

![]()